CQ-LM3S3748 (8) CMSIS (2) ― 2012年11月02日 22時47分44秒

さあ、今日こそ 50MHz で動かすぞ!

と勢い込んでみたものの解決策があるわけではない。

それはそうと TI のlm3s_config.h 、system_lm3s.c 、system_lm4s.c には記述間違いがあるので修正する必要がある。

まずはデータシートの確認からだ。と見始めた途端

・System timer (SysTick), providing a simple, 24-bit clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism

SysTick counter は24ビットだったのだ。動かないのではなくて見かけ上、動いて無いように見えただけか?

SYSDIV = 4 に戻して SysTick_Config の値を24ビット以内に収まるように値を設定する。

コンパイル、実行。

動いた。

いつも簡単な所でつまづいてしまう。原因はデータシートを読まないことだ。

さて、この際だから続けて見ていこう。

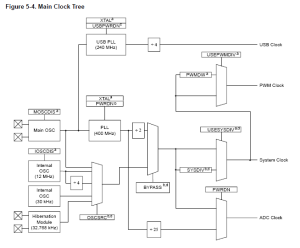

ここまで読んで概略は分かったような気分になった。ちょっと気になるのは Internal OSC や Hibernation Module の出力が PLL に入ってないことだ。PLL の動作範囲内にあるので惜しい気がする。 さて、50MHz で動いたので 動きそうな予感のする 66.67 MHz にも挑戦してみよう。SYSDIV = 3 にしてコンパイル、実行。

あっけなく動いた。

System Clock が 66.67MHz までいったので満足だ。今日はここまでにしておこう。

環境:CQ-LM3S3748

+ CMSIS_LM3S-32.zip

+ TI-CMSIS-Devices-8636.exe

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

と勢い込んでみたものの解決策があるわけではない。

それはそうと TI のlm3s_config.h 、system_lm3s.c 、system_lm4s.c には記述間違いがあるので修正する必要がある。

lm3s_config.h 257行 (Revision 32)

system_lm3s.c 265行 (version V3.00)

system_LM4F.c 265行 (version V3.00)

(CFG_RCC_MOSCDIS << 1)\ 誤

(CFG_RCC_MOSCDIS << 0)\ 正

もちろんこの修正をしたからといって 50MHz で動くわけでは無いだろう。まずはデータシートの確認からだ。と見始めた途端

・System timer (SysTick), providing a simple, 24-bit clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism

SysTick counter は24ビットだったのだ。動かないのではなくて見かけ上、動いて無いように見えただけか?

SYSDIV = 4 に戻して SysTick_Config の値を24ビット以内に収まるように値を設定する。

コンパイル、実行。

動いた。

いつも簡単な所でつまづいてしまう。原因はデータシートを読まないことだ。

さて、この際だから続けて見ていこう。

・If the main oscillator is required, software must enable the main oscillator following reset and allow the main oscillator to stabilize before changing the clock reference. ・If the PLL is being used, the crystal value must be one of the supported frequencies between 3.579545 MHz through 16.384 MHz. ・Possible System Clock Frequencies Using the SYSDIV Field 0x0 /1 reserved Clock source frequency/2 SYSCTL_SYSDIV_1 0x1 /2 reserved Clock source frequency/2 SYSCTL_SYSDIV_2 0x2 /3 reserved Clock source frequency/3 SYSCTL_SYSDIV_3 0x3 /4 50 MHz Clock source frequency/4 SYSCTL_SYSDIV_4 0x4 /5 40 MHz Clock source frequency/5 SYSCTL_SYSDIV_5 0x5 /6 33.33 MHz Clock source frequency/6 SYSCTL_SYSDIV_6 0x6 /7 28.57 MHz Clock source frequency/7 SYSCTL_SYSDIV_7 0x7 /8 25 MHz Clock source frequency/8 SYSCTL_SYSDIV_8 0x8 /9 22.22 MHz Clock source frequency/9 SYSCTL_SYSDIV_9 0x9 /10 20 MHz Clock source frequency/10 SYSCTL_SYSDIV_10 0xA /11 18.18 MHz Clock source frequency/11 SYSCTL_SYSDIV_11 0xB /12 16.67 MHz Clock source frequency/12 SYSCTL_SYSDIV_12 0xC /13 15.38 MHz Clock source frequency/13 SYSCTL_SYSDIV_13 0xD /14 14.29 MHz Clock source frequency/14 SYSCTL_SYSDIV_14 0xE /15 13.33 MHz Clock source frequency/15 SYSCTL_SYSDIV_15 0xF /16 12.5 MHz (default) Clock source frequency/16 SYSCTL_SYSDIV_16なんとなく SYSCTL_SYSDIV_3 でも動きそうな感じだ。

・Initialization and Configuration 1. Bypass the PLL and system clock divider by setting the BYPASS bit and clearing the USESYS bit in the RCC register. This configures the system to run off a “raw” clock source and allows for the new PLL configuration to be validated before switching the system clock to the PLL. 2. Select the crystal value (XTAL) and oscillator source (OSCSRC), and clear the PWRDN bit in RCC/RCC2. Setting the XTAL field automatically pulls valid PLL configuration data for the appropriate crystal, and clearing the PWRDN bit powers and enables the PLL and its output. 3. Select the desired system divider (SYSDIV) in RCC/RCC2 and set the USESYS bit in RCC. The SYSDIV field determines the system frequency for the microcontroller. 4. Wait for the PLL to lock by polling the PLLLRIS bit in the Raw Interrupt Status (RIS) register. 5. Enable use of the PLL by clearing the BYPASS bit in RCC/RCC2.おそらくこのとおりになっているだろう。

・Actual PLL Frequency XTAL Crystal Frequency (MHz) PLL Frequency (MHz) Error 0x04 3.5795 400.904 0.0023% 0x05 3.6864 398.1312 0.0047% 0x06 4.0 400 - 0x07 4.096 401.408 0.0035% 0x08 4.9152 398.1312 0.0047% 0x09 5.0 400 - 0x0A 5.12 399.36 0.0016% 0x0B 6.0 400 - 0x0C 6.144 399.36 0.0016% 0x0D 7.3728 398.1312 0.0047% 0x0E 8.0 400 0.0047% 0x0F 8.192 398.6773333 0.0033% 0x10 10.0 400 - 0x11 12.0 400 -8MHz なのに誤差が出ることになっている。記述ミスだろうか?

ここまで読んで概略は分かったような気分になった。ちょっと気になるのは Internal OSC や Hibernation Module の出力が PLL に入ってないことだ。PLL の動作範囲内にあるので惜しい気がする。 さて、50MHz で動いたので 動きそうな予感のする 66.67 MHz にも挑戦してみよう。SYSDIV = 3 にしてコンパイル、実行。

あっけなく動いた。

System Clock が 66.67MHz までいったので満足だ。今日はここまでにしておこう。

環境:CQ-LM3S3748

+ CMSIS_LM3S-32.zip

+ TI-CMSIS-Devices-8636.exe

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

CQ-LM3S3748 (7) CMSIS (1) ― 2012年10月31日 22時04分46秒

先日コンパイルできなかった core_cm3.c は version V1.10 でかなり古い物だった。新しい物は無いかと探してみると CooCox に CMSIS core for Cortex M3 V1.30 、TI に CMSIS core for Cortex M3 V2.11 があった。

V1.30 には core_cm3.c があるが V2.11 には無い。無くてもよい物なのだろうか?

この際だから一番新しい物を組み合わせることにする。

今回必要なファイルは上記のファイルと startup_gcc.c 、blinky.ld 、blinky.c 。これは以前使った物をそのまま使う。(ベースは CMSIS_LM3S-32.zip の中のもの)

コンパイル、書き込み。

動かない。

怪しいところは見当たらないが system_LM3S.c の PLL を外すと動く。これはクロックの待ち時間が不足していた時の動きに似ている。__NOP() を10個追加して PLL を有効にしてみる。

動かない。

待ち時間だけではなさそうだ。次に SYSDIV を4から16にしてみた。

動いている。 SYSDIV を16から小さくしていくと6までは動く。システムクロックは 400 / 2 / 6 = 33.333MHz となる。

データシートでは 50MHz となっているがそのためには SYSDIV = 4 としなければならない。どうすれば 50MHz で動くんだ?

なかなか簡単には動いてくれない。今日のところは 33.33MHz で勘弁しておいてやろう。

環境:CQ-LM3S3748

+ CMSIS_LM3S-32.zip

+ TI-CMSIS-Devices-8636.exe

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

この際だから一番新しい物を組み合わせることにする。

core_cm3.h Version V3.02 (ARM) core_cmFunc.h Version V3.02 (ARM) core_cmInstr.h Version V3.02 (ARM) LM3S3748.h Version V8636 (TI-CMSIS-Devices-8636.exe) system_LM3S.c Version V3.00 (TI-CMSIS-Devices-8636.exe) system_LM3S.h Version V3.00 (TI-CMSIS-Devices-8636.exe)ところで、ここにある LM3S3748.h は C:\Keil\ARM\INC\Luminary\lm3s3748.h とは別物なので注意が必要だ。V1.10 や V1.30 の lm3s_cmsis.h に相当するものだろう。

今回必要なファイルは上記のファイルと startup_gcc.c 、blinky.ld 、blinky.c 。これは以前使った物をそのまま使う。(ベースは CMSIS_LM3S-32.zip の中のもの)

コンパイル、書き込み。

動かない。

怪しいところは見当たらないが system_LM3S.c の PLL を外すと動く。これはクロックの待ち時間が不足していた時の動きに似ている。__NOP() を10個追加して PLL を有効にしてみる。

動かない。

待ち時間だけではなさそうだ。次に SYSDIV を4から16にしてみた。

動いている。 SYSDIV を16から小さくしていくと6までは動く。システムクロックは 400 / 2 / 6 = 33.333MHz となる。

データシートでは 50MHz となっているがそのためには SYSDIV = 4 としなければならない。どうすれば 50MHz で動くんだ?

なかなか簡単には動いてくれない。今日のところは 33.33MHz で勘弁しておいてやろう。

環境:CQ-LM3S3748

+ CMSIS_LM3S-32.zip

+ TI-CMSIS-Devices-8636.exe

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

CQ-LM3S3748 (6) Using ROM_ functions ― 2012年10月28日 21時01分32秒

LM3S の特色 ROM functions を使ってみる。今回使うファイルを以下に示す。

・startup_gcc.c は CMSIS_LM3S-32.zip の中のもの weak 宣言がしてあるので使いやすい。

・blinky.ld これはどれでもよい。

・SW-EK-LM3S3748-9453.exe の中の driverlib と inc ディレクトリ。適当な場所にコピーする。

・そして blinky.c

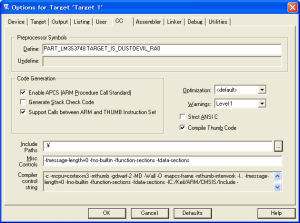

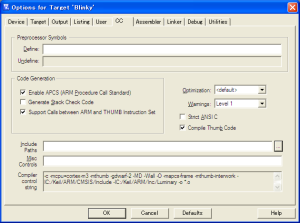

µVision の設定は、ほぼ前回と同じだが CC タブ Preprocessor Symbols の Define: と Include Paths に追加がある。

まず、 Define: はデバイスと Device Class の指定だ。LM3S3748 は Stellaris® DustDevil-class devices になるのでその指定が必要。

では、コンパイル、書き込み。

問題ないようだ。

ここで ROM functions を使った場合と使わない場合のサイズの違いを見てみよう。

5,952 ROM functions(PART_LM3S3748 TARGET_IS_DUSTDEVIL_RA0)

8,640 通常ライブラリ(PART_LM3S3748)

使えば使うほどコンパクトに収まるということか?でも、そのせいで CMSIS との相性が悪くなってしまったようだ。

参照:Stellaris® ソフトウェアの更新

環境:CQ-LM3S3748

+ CMSIS_LM3S-32.zip

+ SW-EK-LM3S3748-9453.exe

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

・startup_gcc.c は CMSIS_LM3S-32.zip の中のもの weak 宣言がしてあるので使いやすい。

・blinky.ld これはどれでもよい。

・SW-EK-LM3S3748-9453.exe の中の driverlib と inc ディレクトリ。適当な場所にコピーする。

・そして blinky.c

µVision の設定は、ほぼ前回と同じだが CC タブ Preprocessor Symbols の Define: と Include Paths に追加がある。

まず、 Define: はデバイスと Device Class の指定だ。LM3S3748 は Stellaris® DustDevil-class devices になるのでその指定が必要。

PART_LM3S3748 TARGET_IS_DUSTDEVIL_RA0そしてヘッダーディレクトリの指定。これは driverlib と inc ディレクトリをどこに置くかによって異なってくるので自分の環境に合わせる。

では、コンパイル、書き込み。

問題ないようだ。

ここで ROM functions を使った場合と使わない場合のサイズの違いを見てみよう。

5,952 ROM functions(PART_LM3S3748 TARGET_IS_DUSTDEVIL_RA0)

8,640 通常ライブラリ(PART_LM3S3748)

使えば使うほどコンパクトに収まるということか?でも、そのせいで CMSIS との相性が悪くなってしまったようだ。

参照:Stellaris® ソフトウェアの更新

環境:CQ-LM3S3748

+ CMSIS_LM3S-32.zip

+ SW-EK-LM3S3748-9453.exe

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

CQ-LM3S3748 (5) SysTick counter ― 2012年10月26日 21時33分30秒

今回は SysTick counter を使ってみる。SW-EK-LM3S3748-9453.exe の中を探してみたが適当なサンプルが見つからない。CMSIS_LM3S-32.zip の中に簡単なサンプルがあるのでこれを使うことにする。ソースを眺めていると前回のサンプルとI/Oアクセスの方法が若干異なることに気がついた。

さてそれでは動かしてみよう。

前回同様変更するのは blinky.ld と blinky.c 。変更する内容もほぼ同じだ。プロジェクトに組み込むファイルは

blinky.c

core_cm3.c

startup_gcc.c

system_lm3s.c

blinky.ld

µVision の設定は前回と同じだ。そしてコンパイル。

あれ!あれ!コンパイルエラーだ。

問題なくコンパイルできる。コンパイラのバージョンが関係しているようだが先を急ぎたいので core_cm3.c をプロジェクトからはずしてみる。

どちらのバージョンでもコンパイルが通る。とりあえずはずしておいて先に進もう。早速 FLASH に書き込んでみるが動かない。

いつもこんな感じだ。

さて、何がいけないの?

シミュレータにかけてみる。

問題ない。

先日の blinky から追加になったのは SystemInit と SysTick なのでその部分を削除してコンパイル、ラン。

動かない。

こうなると泥沼だ。こんな簡単なプログラムなのに...

blinky.c を入れ替えて動かしてみると先日のソースでは問題なく動く。何が異なるのか詳細に見ていくと Delay a few cycles after enabling the peripheral. の部分。違いは

dummy=SYSCTL->RCGC2;

動くではないか。書き込んだレジスタの値を一度読み出さないといけないのか?

この部分のコメントによると数クロックサイクル後にイネーブルになると書いてある。では、ソースを元に戻して nop を4つ追加してみる。

動く。

どうやら待ち時間が足りなかったらしい。それにしてもこんなクリティカルなサンプルを出してくれるとは困ったものだ。そして、 core_cm3.c の問題が残ってしまった。

参照:Stellaris® ソフトウェアの更新

環境:CQ-LM3S3748

+ CMSIS_LM3S-32.zip

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

SW-EK-LM3S3748-9453.exe の blinky

SYSCTL_RCGC2_R = SYSCTL_RCGC2_GPIOF;

CMSIS_LM3S-32.zip の blinky

SYSCTL->RCGC2 |= 0x20;

同じレジスタに値をセットしているが、前者はアドレスに直接、後者は構造体形式だ。もちろん読み込んでいるヘッダーも異なる。検索して圧倒的に多いのは後者のタイプだ。最近はデバイスごとにヘッダーファイルを用意する前者が多いような気がするが Luminary Micro では違うらしい。さてそれでは動かしてみよう。

前回同様変更するのは blinky.ld と blinky.c 。変更する内容もほぼ同じだ。プロジェクトに組み込むファイルは

blinky.c

core_cm3.c

startup_gcc.c

system_lm3s.c

blinky.ld

µVision の設定は前回と同じだ。そしてコンパイル。

あれ!あれ!コンパイルエラーだ。

compiling core_cm3.c... C:\DOCUME~1\ADMINI~1\LOCALS~1\Temp\ccE9GhRB.s: Assembler messages: Error: C:\DOCUME~1\ADMINI~1\LOCALS~1\Temp\ccE9GhRB.s:439: Error: registers may not be the same -- `strexb r0,r0,[r1]' Error: C:\DOCUME~1\ADMINI~1\LOCALS~1\Temp\ccE9GhRB.s:463: Error: registers may not be the same -- `strexh r0,r0,[r1]'Sourcery gcc 4.6.3 を Sourcery gcc 4.5.1 に変更してみる。

問題なくコンパイルできる。コンパイラのバージョンが関係しているようだが先を急ぎたいので core_cm3.c をプロジェクトからはずしてみる。

どちらのバージョンでもコンパイルが通る。とりあえずはずしておいて先に進もう。早速 FLASH に書き込んでみるが動かない。

いつもこんな感じだ。

さて、何がいけないの?

シミュレータにかけてみる。

問題ない。

先日の blinky から追加になったのは SystemInit と SysTick なのでその部分を削除してコンパイル、ラン。

動かない。

こうなると泥沼だ。こんな簡単なプログラムなのに...

blinky.c を入れ替えて動かしてみると先日のソースでは問題なく動く。何が異なるのか詳細に見ていくと Delay a few cycles after enabling the peripheral. の部分。違いは

ulLoop = SYSCTL_RCGC2_R; 前回のソース

__NOP(); 今回のソース

前回と同じように書いて動かしてみる。dummy=SYSCTL->RCGC2;

動くではないか。書き込んだレジスタの値を一度読み出さないといけないのか?

この部分のコメントによると数クロックサイクル後にイネーブルになると書いてある。では、ソースを元に戻して nop を4つ追加してみる。

動く。

どうやら待ち時間が足りなかったらしい。それにしてもこんなクリティカルなサンプルを出してくれるとは困ったものだ。そして、 core_cm3.c の問題が残ってしまった。

参照:Stellaris® ソフトウェアの更新

環境:CQ-LM3S3748

+ CMSIS_LM3S-32.zip

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

CQ-LM3S3748 (4) Password ― 2012年10月24日 20時13分16秒

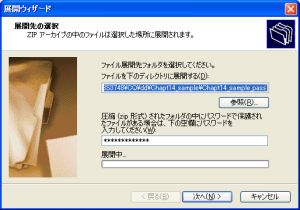

ここまでは比較的順調に進んできた。このあたりでCQ出版のサポート・ページを参照する。ダウンロード・ファイルがたくさん並んでいるがどれが必要な物かわからないので全てダウンロードした。windows_drivers_cq.zip と LM3S3748_board_test.zip は既にダウンロードして使っている。Chapt14_sample.zip には boot_uart_0x1800.zip が入っているらしいのでこの中身を見てみることにする。解凍すると Chapt14_sample_pass.zip と password.txt が入っている。圧縮ファイルの中に圧縮ファイルでさらにパスワードがかかっている。ものすごい念の入れようだ。パスワードを入れて解凍しようとすると

「入力したパスワードが間違っています。もう一度入力してください。」と出てくる。

あれ!間違えたか?

もう一度入力。

だめだ。

確認のため別のファイル(Chapt3_sample.zip)を解凍してみる。

問題ない。解凍できて中身も見ることができる。

どうやら Chapt14_sample_pass.zip は圧縮の時にパスワードを間違って入れてしまったのだろう。

CQ出版に確認してみたいが「ご注意」の中に

”付属マイコン・ボードに関する技術的なサポートや問い合わせはいっさいお受けできません。”

とあるので問い合わせもできないらしい。

Advanced Archive Password Recovery でキーを捜したら 13 Character なので何年かかるかわからない。

困った...

と思っていたら password.txt にパスワードのことが書いてあった。ファイルによってパスワードが異なるのだ。

ああ!何ということだ。

お馬鹿な私。

「入力したパスワードが間違っています。もう一度入力してください。」と出てくる。

あれ!間違えたか?

もう一度入力。

だめだ。

確認のため別のファイル(Chapt3_sample.zip)を解凍してみる。

問題ない。解凍できて中身も見ることができる。

どうやら Chapt14_sample_pass.zip は圧縮の時にパスワードを間違って入れてしまったのだろう。

CQ出版に確認してみたいが「ご注意」の中に

”付属マイコン・ボードに関する技術的なサポートや問い合わせはいっさいお受けできません。”

とあるので問い合わせもできないらしい。

Advanced Archive Password Recovery でキーを捜したら 13 Character なので何年かかるかわからない。

困った...

と思っていたら password.txt にパスワードのことが書いてあった。ファイルによってパスワードが異なるのだ。

ああ!何ということだ。

お馬鹿な私。

CQ-LM3S3748 (3) blinky LED ― 2012年10月22日 21時59分09秒

いつもの LED 点滅からはじめよう。

ベースにしたのは「ファームウェア開発パッケージ」 SW-EK-LM3S3748-9453.exe の boards\ek-lm3s3748\blinky 。変更したのは blinky.c と blinky.ld 。そのまま使ったのは startup_gcc.c 。

blinky.ld は MEMORY の部分のみ変更。オフセット 0x1800 を入れてみた。

blinky.c は port.f0 を port.g2 に変更しただけ。

後は µVision の設定だけだ。

では Target の設定を見ていこう。まず Device 、当然 LM3S3748 を選択。

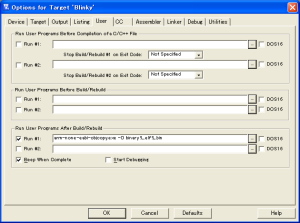

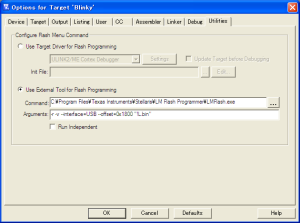

µVision が気に入っている理由のひとつ以下のように外部 Tool が簡単に使えること。ここでは elf file からバイナリファイルを作る。

arm-none-eabi-objcopy.exe -O binary !L.elf !L.bin

Compile Thumb Code にチェックを入れる。

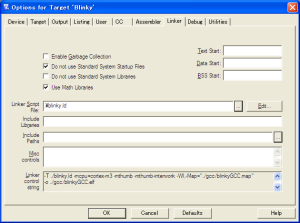

リンカースクリプトファイルを指定する。

ここでも外部 Tool LMFlash.exe が簡単に使える。もちろん Device Database に登録しているのでいちいち書き込む必要もない。

Command: C:\Program Files\Texas Instruments\Stellaris\LM Flash Programmer\LMFlash.exe

Arguments: -r -v --interface=USB --offset=0x1800 "!L.bin"

設定ができたら、コンパイル、書き込み。

どちらもワンクリックだ。

クリック直後に LED が点滅する。書き込みも高速だ。

いいね~。

環境:CQ-LM3S3748

+ SW-EK-LM3S3748-9453.exe

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

ベースにしたのは「ファームウェア開発パッケージ」 SW-EK-LM3S3748-9453.exe の boards\ek-lm3s3748\blinky 。変更したのは blinky.c と blinky.ld 。そのまま使ったのは startup_gcc.c 。

blinky.ld は MEMORY の部分のみ変更。オフセット 0x1800 を入れてみた。

変更前

MEMORY

{

FLASH (rx) : ORIGIN = 0x00000000, LENGTH = 0x00020000

SRAM (rwx) : ORIGIN = 0x20000000, LENGTH = 0x00010000

}

変更後

MEMORY

{

FLASH (rx) : ORIGIN = 0x00001800, LENGTH = 0x0001E800

SRAM (rwx) : ORIGIN = 0x20000000, LENGTH = 0x00010000

}blinky.c は port.f0 を port.g2 に変更しただけ。

後は µVision の設定だけだ。

では Target の設定を見ていこう。まず Device 、当然 LM3S3748 を選択。

µVision が気に入っている理由のひとつ以下のように外部 Tool が簡単に使えること。ここでは elf file からバイナリファイルを作る。

arm-none-eabi-objcopy.exe -O binary !L.elf !L.bin

Compile Thumb Code にチェックを入れる。

リンカースクリプトファイルを指定する。

ここでも外部 Tool LMFlash.exe が簡単に使える。もちろん Device Database に登録しているのでいちいち書き込む必要もない。

Command: C:\Program Files\Texas Instruments\Stellaris\LM Flash Programmer\LMFlash.exe

Arguments: -r -v --interface=USB --offset=0x1800 "!L.bin"

設定ができたら、コンパイル、書き込み。

どちらもワンクリックだ。

クリック直後に LED が点滅する。書き込みも高速だ。

いいね~。

環境:CQ-LM3S3748

+ SW-EK-LM3S3748-9453.exe

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

CQ-LM3S3748 (2) ― 2012年10月21日 20時23分50秒

二日間にわたってクリックを続けた結果「ファームウェア開発パッケージ」 と「Stellaris® フラッシュ・プログラマ、GUI およびコマンド・ライン」は無事ダウンロードできた。ダウンロードのボタンをクリックし続けているとそのうちダウンロードメニューが出てくる。その時すかさずダウンロード。最初の段階でこんなに苦労するとは思わなかった。

まずはダウンロードした「ファームウェア開発パッケージ」 の中身を見てみよう。

サンプル、ライブラリ、ドライバと盛りだくさんだ。プロジェクトも IAR KEIL CCS GCC と一般的なものはそろっている。しかし、CMSIS は採用してないようだ。

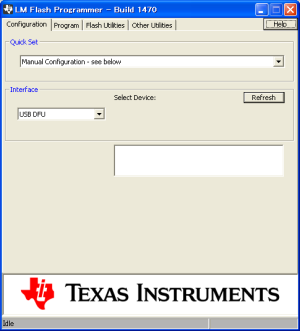

もうひとつのソフト「フラッシュプログラマ」はよくできたソフトだ。多機能で使いやすい。他のメーカもこんなライターソフトを出してほしいものだ。

そうこうしているうちに注文していた基板が届いた。いや、本が届いた。 特別変わった基板ではないがプッシュスイッチが2個実装されている。リセットスイッチはありがたい。もうひとつは何だろう?とりあえず付属の本を読んでみる。Pawn という単語がたくさん出てくる。Pawn という言語らしいが使うつもりは無いので読み飛ばす。

わかったこと

・Stellaris Ware が ROM に内蔵されている。

・ROM には Serial Boot Loader が内蔵されている。

・Serial Boot Loader は UART0 、SSI0 、I2C0 のいずれかを使う。

・USB ブートローダーがフラッシュROMに書き込んである。

・アプリケーションプログラムは 0x00001800 - 0x0001FFFF の範囲。

・フラッシュプログラマは bin フォーマットのみ受け付ける。

なんとなく STM32 に似ているような気がする。

さて、0x1800 のオフセットはどうすればいいんだっけ?

参照:超入門!付属ARMマイコンで始めるロボット製作

まずはダウンロードした「ファームウェア開発パッケージ」 の中身を見てみよう。

サンプル、ライブラリ、ドライバと盛りだくさんだ。プロジェクトも IAR KEIL CCS GCC と一般的なものはそろっている。しかし、CMSIS は採用してないようだ。

もうひとつのソフト「フラッシュプログラマ」はよくできたソフトだ。多機能で使いやすい。他のメーカもこんなライターソフトを出してほしいものだ。

そうこうしているうちに注文していた基板が届いた。いや、本が届いた。 特別変わった基板ではないがプッシュスイッチが2個実装されている。リセットスイッチはありがたい。もうひとつは何だろう?とりあえず付属の本を読んでみる。Pawn という単語がたくさん出てくる。Pawn という言語らしいが使うつもりは無いので読み飛ばす。

わかったこと

・Stellaris Ware が ROM に内蔵されている。

・ROM には Serial Boot Loader が内蔵されている。

・Serial Boot Loader は UART0 、SSI0 、I2C0 のいずれかを使う。

・USB ブートローダーがフラッシュROMに書き込んである。

・アプリケーションプログラムは 0x00001800 - 0x0001FFFF の範囲。

・フラッシュプログラマは bin フォーマットのみ受け付ける。

なんとなく STM32 に似ているような気がする。

さて、0x1800 のオフセットはどうすればいいんだっけ?

参照:超入門!付属ARMマイコンで始めるロボット製作

CQ-LM3S3748 (1) 超入門!付属ARMマイコンで始めるロボット製作 ― 2012年10月18日 21時53分52秒

amazon のギフト券をもらったので何に使おうかと使い道を考えていた。いろいろ探していて見つけたのが 「超入門!付属ARMマイコンで始めるロボット製作」。2012/3/21発売、とあるからずいぶん前に発売になっている。しかし、気がつかなかった。本屋さんにもよく行くが見た記憶がない。CQ出版社のホームページからこの本を見つけるのもきわめて困難だ。サポートページに至ってはどこから入るのかさえ分からない。

さて、問題の CPU は LM3S3748 。前から Luminary Micro のものがほしかったのでちょうどよかった。しかし、高価だ ¥3780 なり。ポチ。

次に TI のサイトでデータシートを手に入れる。さらに「ファームウェア開発パッケージ」 、「キット CD、EKC-LM3S3748、CodeSourcery ツール付き」、「Stellaris® フラッシュ・プログラマ、GUI およびコマンド・ライン」をダウンロードしようとするがダウンロードできない。ダウンロードの仕方が分からないといったほうがよいかもしれない。なかなか手ごわいぞ TI 。

参照:超入門!付属ARMマイコンで始めるロボット製作

さて、問題の CPU は LM3S3748 。前から Luminary Micro のものがほしかったのでちょうどよかった。しかし、高価だ ¥3780 なり。ポチ。

次に TI のサイトでデータシートを手に入れる。さらに「ファームウェア開発パッケージ」 、「キット CD、EKC-LM3S3748、CodeSourcery ツール付き」、「Stellaris® フラッシュ・プログラマ、GUI およびコマンド・ライン」をダウンロードしようとするがダウンロードできない。ダウンロードの仕方が分からないといったほうがよいかもしれない。なかなか手ごわいぞ TI 。

•Please take a moment to review your information. We are sorry but your transaction was unable to be processed. We apologize for the inconvenience. Please try again later.

参照:超入門!付属ARMマイコンで始めるロボット製作

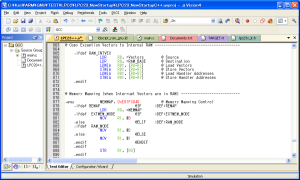

Keil µVision4 + GCC (3) LPC2300 (3) Interrupt Vectors are in RAM ― 2012年10月16日 19時01分32秒

さて、気になっていた RAM 上に Vectors をコピーして動かすという件だ。ソースをながめると RAM_INTVEC 、 REMAP 、 RAM_MODE を定義すれば目的は達せられるようだ。コンパイルしてみる。

LPC2300.s(865): error: undefined symbol Vectors used as an immediate value

なるほどラベルが無い。 Vectors をベクターの先頭に追加する。再びコンパイル。

LPC2300.s(865): error: symbol .cs3.interrupt_vector is in a different section

セクションが異なるとアクセスできないのか?

コンパイルは通るが動かない。シミュレータで見ると main に入った途端せっかく書いたベクターがクリアされてしまう。RAM の先頭 0x40 バイトを空けなくてはならないのだ。 .space を入れてみる。

今度はエリアを強制的に空ける。リンカースクリプトの変更だ。

ram (rwx) : ORIGIN = 0x40000040, LENGTH = 64K-0x40

シミュレータではうまく動く。基板に書き込んでみても動く。しかし、実際に RAM 上のベクターテーブルで動いているのかどうかは確認のしようが無い。では、これで何ができるんだというと RAM 上にあるので書き換えができる。或いは FLASH 上に Monitor をおいて RAM でプログラムを実行できる。といった所だろうか。

環境:CQ-FRK-NXP-ARM

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

LPC2300.s(865): error: undefined symbol Vectors used as an immediate value

なるほどラベルが無い。 Vectors をベクターの先頭に追加する。再びコンパイル。

LPC2300.s(865): error: symbol .cs3.interrupt_vector is in a different section

セクションが異なるとアクセスできないのか?

ADR R8, Vectors を

LDR R8, =Vectors に変更するコンパイルは通るが動かない。シミュレータで見ると main に入った途端せっかく書いたベクターがクリアされてしまう。RAM の先頭 0x40 バイトを空けなくてはならないのだ。 .space を入れてみる。

.section ".cs3.region-head.ram","wx"

.globl _RAM_INTVEC_

.type _RAM_INTVEC_, %object

_RAM_INTVEC_: .space 0x40

.size _RAM_INTVEC_, . - _RAM_INTVEC_

やはり main に入った途端ベクターがクリアされてしまう。これは却下。今度はエリアを強制的に空ける。リンカースクリプトの変更だ。

ram (rwx) : ORIGIN = 0x40000040, LENGTH = 64K-0x40

シミュレータではうまく動く。基板に書き込んでみても動く。しかし、実際に RAM 上のベクターテーブルで動いているのかどうかは確認のしようが無い。では、これで何ができるんだというと RAM 上にあるので書き換えができる。或いは FLASH 上に Monitor をおいて RAM でプログラムを実行できる。といった所だろうか。

環境:CQ-FRK-NXP-ARM

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

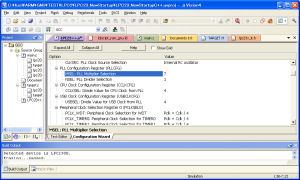

Keil µVision4 + GCC (3) LPC2300 (2) Clock Setup ― 2012年10月14日 20時58分54秒

修正した LPC2300.s がうまく動いた所でコンフィギュレーションウィザードを使ってPLLの設定をいろいろ変えて確認する。

その前にLPC2388のデータシートで概略を見てみよう。

・ARM7TDMI-S processor, running at up to 72 MHz.

・The flash memory is 128 bits wide and includes pre-fetching and buffering techniques to allow it to operate at SRAM speeds of 72 MHz.

・The nominal IRC frequency is 4 MHz.

・The PLL input, in the range of 32 kHz to 25 MHz.

・The resulting frequency must be in the range of 275 MHz to 550 MHz.

・CCLKCFG(CCLKSEL) is only 0 and odd values (1, 3, 5, ..., 255)

・a value ‘M’, in the range of 1 through 32768.

・a value ‘N’, which may be in the range of 1 to 256.

・MAMCR

0 - MAM functions disabled

1 - MAM functions partially enabled

2 - MAM functions fully enabled

・MAMTIM

1 - For a system clock slower than 20 MHz.

2 - For a system clock between 20 MHz and 40 MHz.

3 - For a system clock between 40 MHz and 60 MHz.

4 - For system clocks of 60 MHz and above..

Datasheet と User manual では書いてある数値が異なる場合があるが主に Datasheet の記述を引用している。

さて、ここで気になるのは動作クロックとPLL出力周波数の最大と最小はどのくらいになるかということだ。幸いPLLを使えばクロックは自由に設定できるので気軽に試すことができる。

まず、PLL出力周波数 (Fcco) の最小値は?

Fcco = Foscx2xM/N = 4x2x7/1 = 56MHz

Fcclk = Fcclk/PCLK_TIMER0 = Fcco/CCLKSEL = 56/4 = 14MHz

PCLK = 14/4 = 3.5MHz

確認のため T0MR0 に 1750000-1 を設定して点滅速度で確認する。

結果:問題なく動作

それでは、PLL出力周波数 (Fcco) の最大値は?

Fcco = Foscx2xM/N = 4x2x130/1 = 1040MHz

Fcclk = Fcco/CCLKSEL = 1040/16 = 65MHz

PCLK = Fcclk/PCLK_TIMER0 = 65/1 = 65MHz

確認のため T0MR0 に 32500000-1 を設定して点滅速度で確認する。

結果:問題なく動作

最後は動作クロック (Fcclk) の最大値は?

Fcco = Foscx2xM/N = 4x2x58/1 = 464MHz

Fcclk = Fcco/CCLKSEL = 464/4 = 116MHz

PCLK = Fcclk/PCLK_TIMER0 = 116/1 = 116MHz

確認のため T0MR0 に 58000000-1 を設定して点滅速度で確認する。

結果:問題なく動作

少しは余裕があると思っていたが結構余裕があるものだ。ただし、Fcclk 116MHz になると MAMCR=0 MAMTIM=7 でしか動かない。従って、MAMCR=2 MAMTIM=3 で動く Fcclk 100MHz あたりが一番高速なのかもしれない。そして、細かく設定を変えて試したい場合必要な部分だけ簡単に変更できるコンフィギュレーションウィザードはありがたかった。しかし、自分で書くとなると頭が痛くなる。あまりなじみの無い書式だ。

環境:CQ-FRK-NXP-ARM

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

その前にLPC2388のデータシートで概略を見てみよう。

・ARM7TDMI-S processor, running at up to 72 MHz.

・The flash memory is 128 bits wide and includes pre-fetching and buffering techniques to allow it to operate at SRAM speeds of 72 MHz.

・The nominal IRC frequency is 4 MHz.

・The PLL input, in the range of 32 kHz to 25 MHz.

・The resulting frequency must be in the range of 275 MHz to 550 MHz.

・CCLKCFG(CCLKSEL) is only 0 and odd values (1, 3, 5, ..., 255)

・a value ‘M’, in the range of 1 through 32768.

・a value ‘N’, which may be in the range of 1 to 256.

・MAMCR

0 - MAM functions disabled

1 - MAM functions partially enabled

2 - MAM functions fully enabled

・MAMTIM

1 - For a system clock slower than 20 MHz.

2 - For a system clock between 20 MHz and 40 MHz.

3 - For a system clock between 40 MHz and 60 MHz.

4 - For system clocks of 60 MHz and above..

Datasheet と User manual では書いてある数値が異なる場合があるが主に Datasheet の記述を引用している。

さて、ここで気になるのは動作クロックとPLL出力周波数の最大と最小はどのくらいになるかということだ。幸いPLLを使えばクロックは自由に設定できるので気軽に試すことができる。

まず、PLL出力周波数 (Fcco) の最小値は?

OSC=RCosc M=7 N=1 CCLKSEL=4 PCLK_TIMER0=0 (1/4)Mが7未満では動かないので上記の設定が最小値になる。

Fcco = Foscx2xM/N = 4x2x7/1 = 56MHz

Fcclk = Fcclk/PCLK_TIMER0 = Fcco/CCLKSEL = 56/4 = 14MHz

PCLK = 14/4 = 3.5MHz

確認のため T0MR0 に 1750000-1 を設定して点滅速度で確認する。

結果:問題なく動作

それでは、PLL出力周波数 (Fcco) の最大値は?

OSC=RCosc M=130 N=1 CCLKSEL=16 PCLK_TIMER0=1(1/1)Mが141までは動くが点滅速度が逆に遅くなるのでPLLがうまく動作していないのだろう。従って、上記の設定を最大値ということにする。

Fcco = Foscx2xM/N = 4x2x130/1 = 1040MHz

Fcclk = Fcco/CCLKSEL = 1040/16 = 65MHz

PCLK = Fcclk/PCLK_TIMER0 = 65/1 = 65MHz

確認のため T0MR0 に 32500000-1 を設定して点滅速度で確認する。

結果:問題なく動作

最後は動作クロック (Fcclk) の最大値は?

OSC=RCosc M=58 N=1 CCLKSEL=4 PCLK_TIMER0=1(1/1)Mが59になると動かないので上記の設定が最大値ということになる。

Fcco = Foscx2xM/N = 4x2x58/1 = 464MHz

Fcclk = Fcco/CCLKSEL = 464/4 = 116MHz

PCLK = Fcclk/PCLK_TIMER0 = 116/1 = 116MHz

確認のため T0MR0 に 58000000-1 を設定して点滅速度で確認する。

結果:問題なく動作

少しは余裕があると思っていたが結構余裕があるものだ。ただし、Fcclk 116MHz になると MAMCR=0 MAMTIM=7 でしか動かない。従って、MAMCR=2 MAMTIM=3 で動く Fcclk 100MHz あたりが一番高速なのかもしれない。そして、細かく設定を変えて試したい場合必要な部分だけ簡単に変更できるコンフィギュレーションウィザードはありがたかった。しかし、自分で書くとなると頭が痛くなる。あまりなじみの無い書式だ。

環境:CQ-FRK-NXP-ARM

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

最近のコメント