CQ-LM3S3748 (8) CMSIS (2) ― 2012年11月02日 22時47分44秒

さあ、今日こそ 50MHz で動かすぞ!

と勢い込んでみたものの解決策があるわけではない。

それはそうと TI のlm3s_config.h 、system_lm3s.c 、system_lm4s.c には記述間違いがあるので修正する必要がある。

まずはデータシートの確認からだ。と見始めた途端

・System timer (SysTick), providing a simple, 24-bit clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism

SysTick counter は24ビットだったのだ。動かないのではなくて見かけ上、動いて無いように見えただけか?

SYSDIV = 4 に戻して SysTick_Config の値を24ビット以内に収まるように値を設定する。

コンパイル、実行。

動いた。

いつも簡単な所でつまづいてしまう。原因はデータシートを読まないことだ。

さて、この際だから続けて見ていこう。

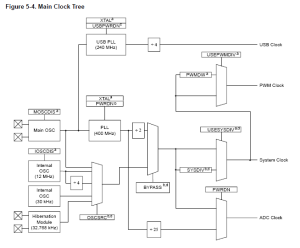

ここまで読んで概略は分かったような気分になった。ちょっと気になるのは Internal OSC や Hibernation Module の出力が PLL に入ってないことだ。PLL の動作範囲内にあるので惜しい気がする。 さて、50MHz で動いたので 動きそうな予感のする 66.67 MHz にも挑戦してみよう。SYSDIV = 3 にしてコンパイル、実行。

あっけなく動いた。

System Clock が 66.67MHz までいったので満足だ。今日はここまでにしておこう。

環境:CQ-LM3S3748

+ CMSIS_LM3S-32.zip

+ TI-CMSIS-Devices-8636.exe

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

と勢い込んでみたものの解決策があるわけではない。

それはそうと TI のlm3s_config.h 、system_lm3s.c 、system_lm4s.c には記述間違いがあるので修正する必要がある。

lm3s_config.h 257行 (Revision 32)

system_lm3s.c 265行 (version V3.00)

system_LM4F.c 265行 (version V3.00)

(CFG_RCC_MOSCDIS << 1)\ 誤

(CFG_RCC_MOSCDIS << 0)\ 正

もちろんこの修正をしたからといって 50MHz で動くわけでは無いだろう。まずはデータシートの確認からだ。と見始めた途端

・System timer (SysTick), providing a simple, 24-bit clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism

SysTick counter は24ビットだったのだ。動かないのではなくて見かけ上、動いて無いように見えただけか?

SYSDIV = 4 に戻して SysTick_Config の値を24ビット以内に収まるように値を設定する。

コンパイル、実行。

動いた。

いつも簡単な所でつまづいてしまう。原因はデータシートを読まないことだ。

さて、この際だから続けて見ていこう。

・If the main oscillator is required, software must enable the main oscillator following reset and allow the main oscillator to stabilize before changing the clock reference. ・If the PLL is being used, the crystal value must be one of the supported frequencies between 3.579545 MHz through 16.384 MHz. ・Possible System Clock Frequencies Using the SYSDIV Field 0x0 /1 reserved Clock source frequency/2 SYSCTL_SYSDIV_1 0x1 /2 reserved Clock source frequency/2 SYSCTL_SYSDIV_2 0x2 /3 reserved Clock source frequency/3 SYSCTL_SYSDIV_3 0x3 /4 50 MHz Clock source frequency/4 SYSCTL_SYSDIV_4 0x4 /5 40 MHz Clock source frequency/5 SYSCTL_SYSDIV_5 0x5 /6 33.33 MHz Clock source frequency/6 SYSCTL_SYSDIV_6 0x6 /7 28.57 MHz Clock source frequency/7 SYSCTL_SYSDIV_7 0x7 /8 25 MHz Clock source frequency/8 SYSCTL_SYSDIV_8 0x8 /9 22.22 MHz Clock source frequency/9 SYSCTL_SYSDIV_9 0x9 /10 20 MHz Clock source frequency/10 SYSCTL_SYSDIV_10 0xA /11 18.18 MHz Clock source frequency/11 SYSCTL_SYSDIV_11 0xB /12 16.67 MHz Clock source frequency/12 SYSCTL_SYSDIV_12 0xC /13 15.38 MHz Clock source frequency/13 SYSCTL_SYSDIV_13 0xD /14 14.29 MHz Clock source frequency/14 SYSCTL_SYSDIV_14 0xE /15 13.33 MHz Clock source frequency/15 SYSCTL_SYSDIV_15 0xF /16 12.5 MHz (default) Clock source frequency/16 SYSCTL_SYSDIV_16なんとなく SYSCTL_SYSDIV_3 でも動きそうな感じだ。

・Initialization and Configuration 1. Bypass the PLL and system clock divider by setting the BYPASS bit and clearing the USESYS bit in the RCC register. This configures the system to run off a “raw” clock source and allows for the new PLL configuration to be validated before switching the system clock to the PLL. 2. Select the crystal value (XTAL) and oscillator source (OSCSRC), and clear the PWRDN bit in RCC/RCC2. Setting the XTAL field automatically pulls valid PLL configuration data for the appropriate crystal, and clearing the PWRDN bit powers and enables the PLL and its output. 3. Select the desired system divider (SYSDIV) in RCC/RCC2 and set the USESYS bit in RCC. The SYSDIV field determines the system frequency for the microcontroller. 4. Wait for the PLL to lock by polling the PLLLRIS bit in the Raw Interrupt Status (RIS) register. 5. Enable use of the PLL by clearing the BYPASS bit in RCC/RCC2.おそらくこのとおりになっているだろう。

・Actual PLL Frequency XTAL Crystal Frequency (MHz) PLL Frequency (MHz) Error 0x04 3.5795 400.904 0.0023% 0x05 3.6864 398.1312 0.0047% 0x06 4.0 400 - 0x07 4.096 401.408 0.0035% 0x08 4.9152 398.1312 0.0047% 0x09 5.0 400 - 0x0A 5.12 399.36 0.0016% 0x0B 6.0 400 - 0x0C 6.144 399.36 0.0016% 0x0D 7.3728 398.1312 0.0047% 0x0E 8.0 400 0.0047% 0x0F 8.192 398.6773333 0.0033% 0x10 10.0 400 - 0x11 12.0 400 -8MHz なのに誤差が出ることになっている。記述ミスだろうか?

ここまで読んで概略は分かったような気分になった。ちょっと気になるのは Internal OSC や Hibernation Module の出力が PLL に入ってないことだ。PLL の動作範囲内にあるので惜しい気がする。 さて、50MHz で動いたので 動きそうな予感のする 66.67 MHz にも挑戦してみよう。SYSDIV = 3 にしてコンパイル、実行。

あっけなく動いた。

System Clock が 66.67MHz までいったので満足だ。今日はここまでにしておこう。

環境:CQ-LM3S3748

+ CMSIS_LM3S-32.zip

+ TI-CMSIS-Devices-8636.exe

+ Keil MDK-ARM V4.53

+ GCC Sourcery CodeBench Lite 2012.03-56

+ KPIT Cummins GNU-Archive Editor v1.1

+ KPIT Cummins GNU-Map Viewer v1.0

最近のコメント